18202964122

为了保持先进制程IC的良率,“失效分析”有其相当的需求性。

现今IC 产业发展的趋势中,先进制程一直扮演着先躯的角色,靠着台积电独步全球的研发能力,使摩尔定律得以续命。而先进制程的特点除了元件缩小、相同面积可塞进更多的晶体管以外,还具有较快的反应时间,因此采用先进制程的IC 皆是应用在需要大量运算的产品类型上,比如手机处理器、绘图处理器、资料中心服务器或采矿机等。

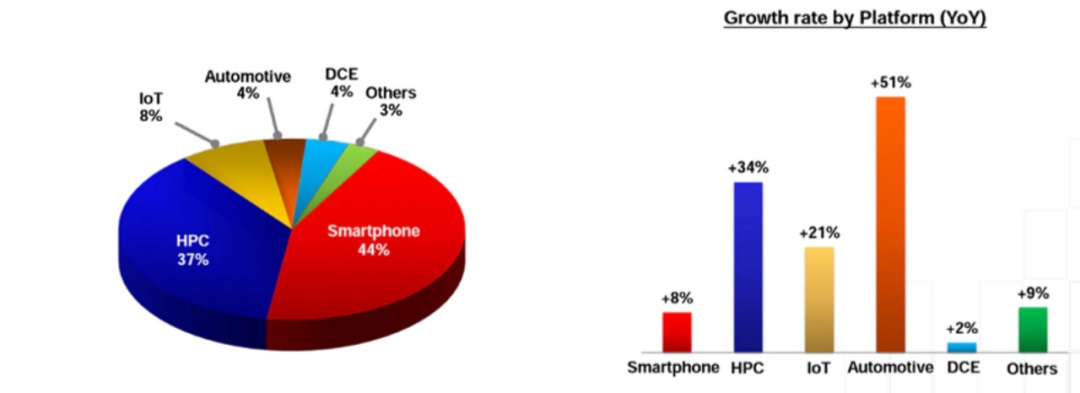

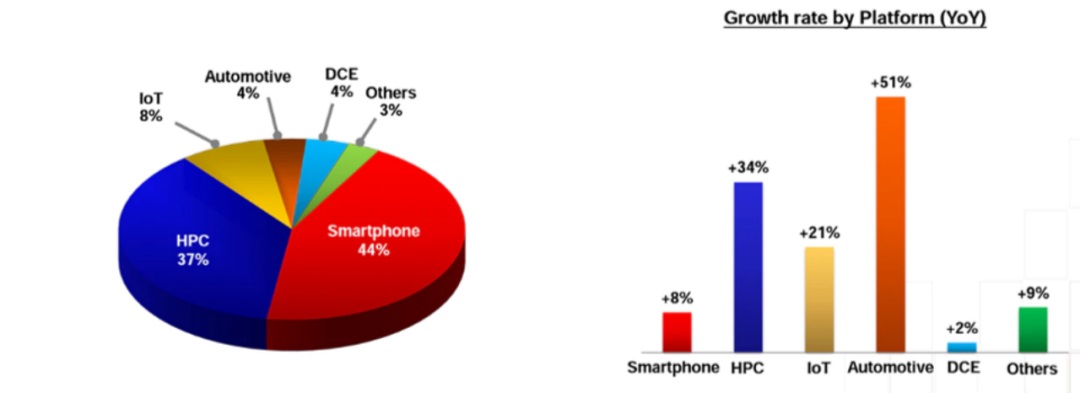

以台积电为例,在产品划分上可明显看出此类IC 在营收中占有举足轻重的地位。图一即是2021 年台积电5 大产品类型的占比,其中高性能计算(High Performance Computing, HPC)的营收占比不仅达37%,其增长率也高达34%,现今的规模与未来的成长皆相当可观。而不只是台积电,为了保持先进制程IC 的良率,“失效分析”势必有其相当的需求性。

由于先进制程的 IC 具备几个结构与材料上的特点,比如电路设计的复杂程度、较大的 die size、采用先进的封装、立体的FinFET 鳍式场效晶体管元件、特殊的 metal 与介电材质等等,相较于传统制程的设计,再增加失效分析上的难度。借着新型机台诞生与分析技术的开发,闳康科技已在先进制程分析上掌握关键技术,以下将针对各种分析技术一一说明。

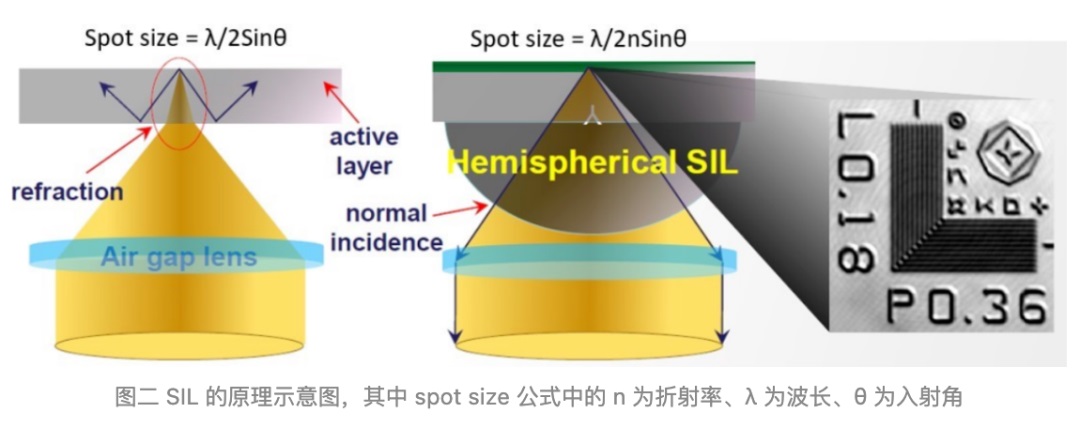

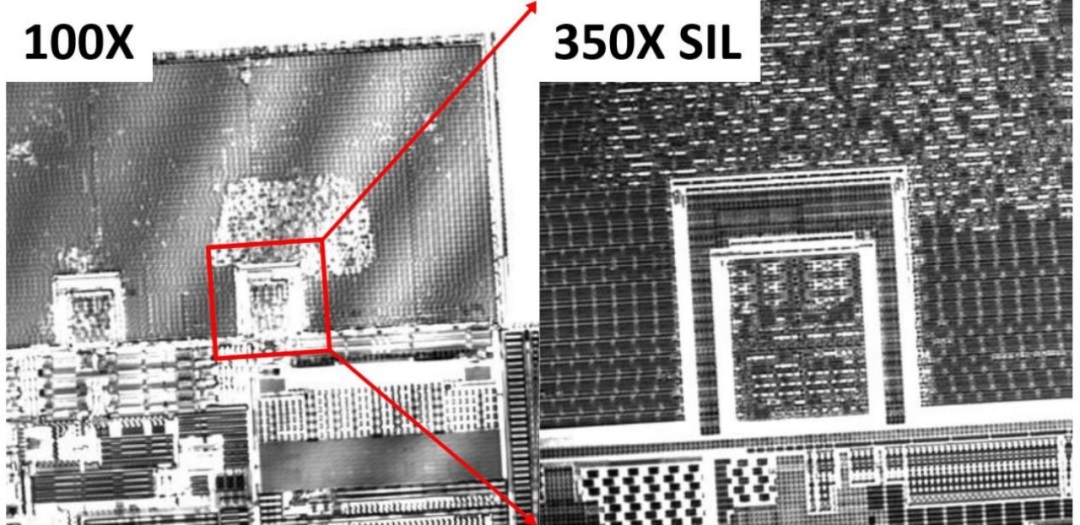

Solid Immersion Lens(SIL)是一半球型高折射率的固态材料固定在镜头前方,拍摄时需贴附在样品上,其目的是在增加数值口径(Numerical Aperture, NA),即增加集光力,进而提高解析度,达成先进制程精密定位之要求,提升后续寻找缺陷的成功率。图二说明SIL 的原理,借着半球型的SIL 扩展了集光的角度,也就是增加了NA 值,另外从spot size 的公式也可清楚地了解到,配备SIL 的镜头具有较小的spot size,可辨认更小的尺寸,因此传统镜头的物镜倍率只能到100 倍,而SIL 镜头的倍率可高达350 倍,解析能力立刻比传统的定位方式提升3.5 倍,图三即显示了此镜头的优异性,即便是5nm 的产品,也可清楚地定位到单一元件。

研磨技术

在集成电路失效分析的流程中,定位完成后通常是进行去层的样品制备,但制程越来越小,金属介电层(inter-metal dielectric, IMD)也越来越薄,每一层的去除考验着人员的经验与细心,另外缓冲层氮化钽(TaN)与低介电常数介电层的使用造成了严重研磨的层差,使得观察范围变得非常狭窄。靠着闳康科技研发团队锲而不舍的精神,研发出特殊化学配方,可以解决层差的问题,终于让观察范围扩大几百 um 的大小。

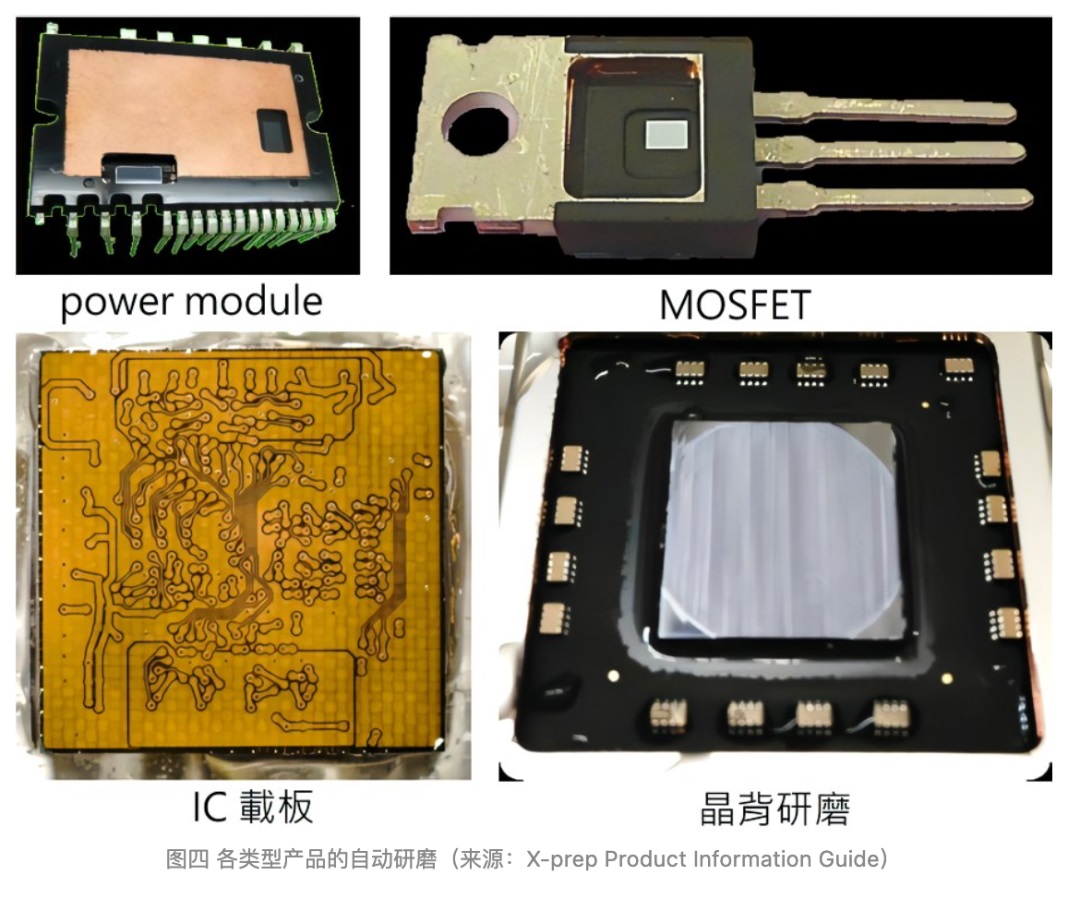

晶背减薄在亮点定位上是常用的手法,尤其先进制程的金属层高达十几层,不易由芯片正面测得亮点,而封装的方式也常采用覆晶式(flip-chip)的架构,再加上先进制程的发光效率不若传统制程,所以晶背亮点使用得非常频繁。当然晶背减薄在先进制程上成为必经的样品制备手段,但是当晶背厚度到了100um 以下时,芯片的翘曲(warpage)便会产生,研磨上的应力就易造成 die crack (晶粒破裂)的问题。闳康科技的自动研磨机台可以依芯片的翘曲程度自动调整,减少制备失败的风险、增加研磨的平坦度,更重要的是,此自动研磨机具有量测厚度的功能,可以精准将厚度控制在1um 的范围内。前文提及的 SIL 镜头对芯片厚度是有要求的,因此 SIL 镜头和自动研磨机是非常速配的组合,甚至未来到了需要用到晶背可见光定位技术的时候,芯片必须降至低于5um 这么薄的厚度,此时更非自动研磨机不可了。除了应用于晶背研磨,其它诸如芯片正面与封装结构皆可运用,应用极其广泛。

在芯片去层的方法中,除了手动研磨以外,P-FIB delayer(去层)是另外一种选择,P-FIB 是利用氙离子进行大范围的平面蚀刻,最大可达200um x 200um,它除了可符合平坦度的要求以外,最重要的一点是它可降低积碳的现象。

所谓积碳是指样品在处理过程中,会经过化学药剂和研磨液的处理、沾染一些微不可见的脏污,这些非样品本身的外来物主要是碳氢化合物的组成,即便在清洁后,多少还是会在芯片上残留。例如在SEM 下经过电子束的照射,碳氢键结被打断,在样品上溅镀碳的污染物。这个非预期的溅镀层不但会干扰观察,更会影响后文将提及的纳米探针(nano-probe)的接触,因此先进制程中如果要进行nano-probe 的话,P-FIB delayer 是绝对必要的一个步骤。 图五 先进制程利用 P-FIB delayer 的范围与显示的 via 层

图五 先进制程利用 P-FIB delayer 的范围与显示的 via 层

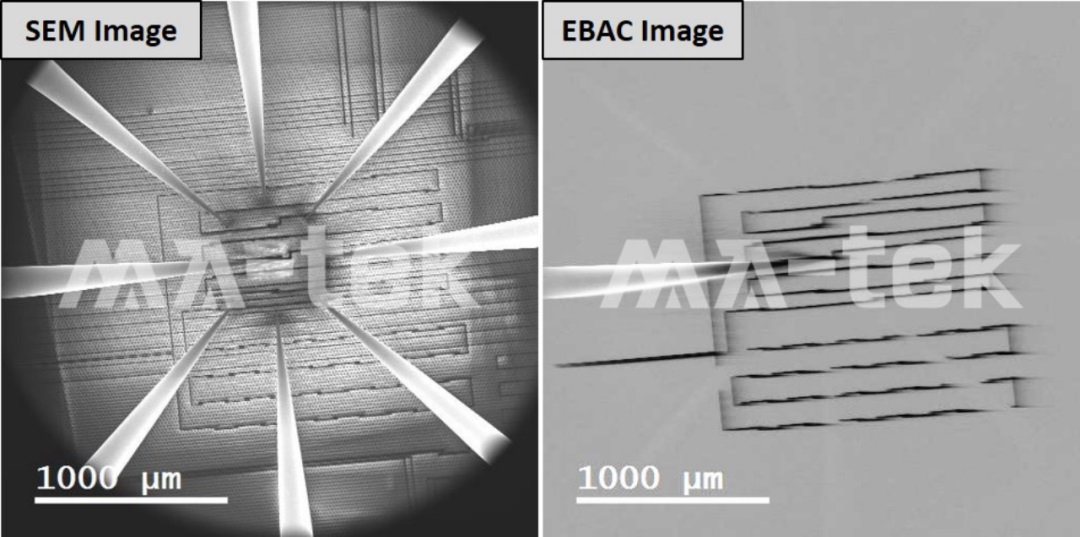

EBAC(Electron Beam Absorbed Current)

数位电路为了在测试时就能筛选出问题,会在电路上加进 DFT(design for test)的设计,经过此测试会得出可能的失效路径叫做 scan path,此缺陷可能产生在此路径上的任何位置,此路径经由interconnect 即metal / via 的走线传递讯号,传统上通常会采取逐层去除、逐层观察的方式找出缺陷,可想而知,这种土法炼钢的方式随着观察区域变大、线径缩小,成功率将大幅下降。

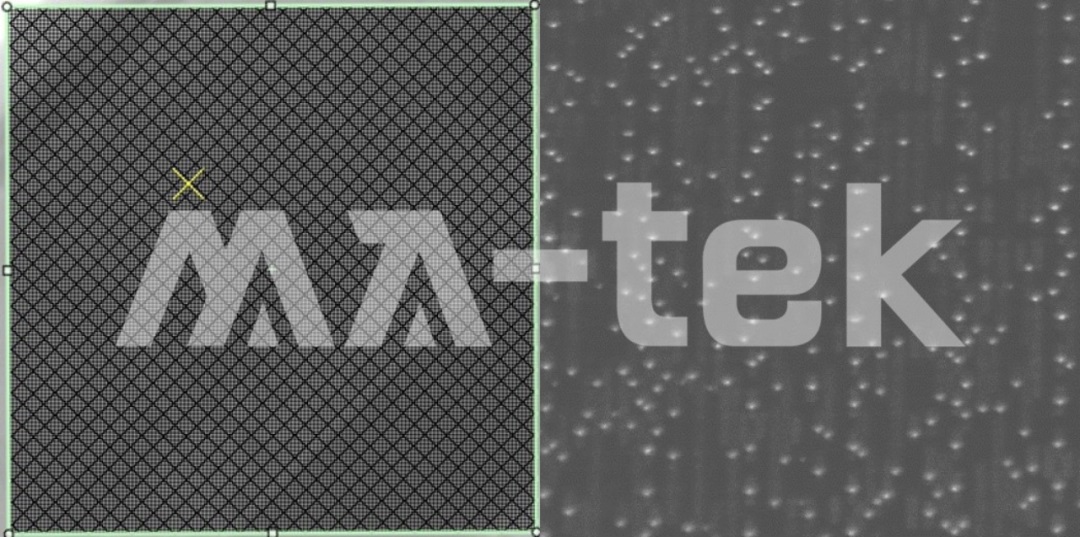

为了测定出确切的缺陷位置,最有效的方式是在动态测试时进行亮点定位,最常见的有 LVP(laser voltage probing)与 TRE(time-resolved emission),但此类验证方式对大多数公司来说花费昂贵,而EBAC 既然可以显示出interconnect 的绕线路径,那么此技术就有可能找出绕线的缺陷,抓出scan fail 的故障真因。因此,如果能从测试中先找出有问题的讯号,即可利用EBAC 在此讯号对应到的metal line 上扎针,定位出可能的缺陷位置,在数位电路上的失效分析不失为一项利器,尤其是运用在更先进的制程上。 图六 EBAC可以显示与扎针处相连如迷宫般的 metal 走线

图六 EBAC可以显示与扎针处相连如迷宫般的 metal 走线

EBIRCH(Electron Beam Induced Resistance Change)

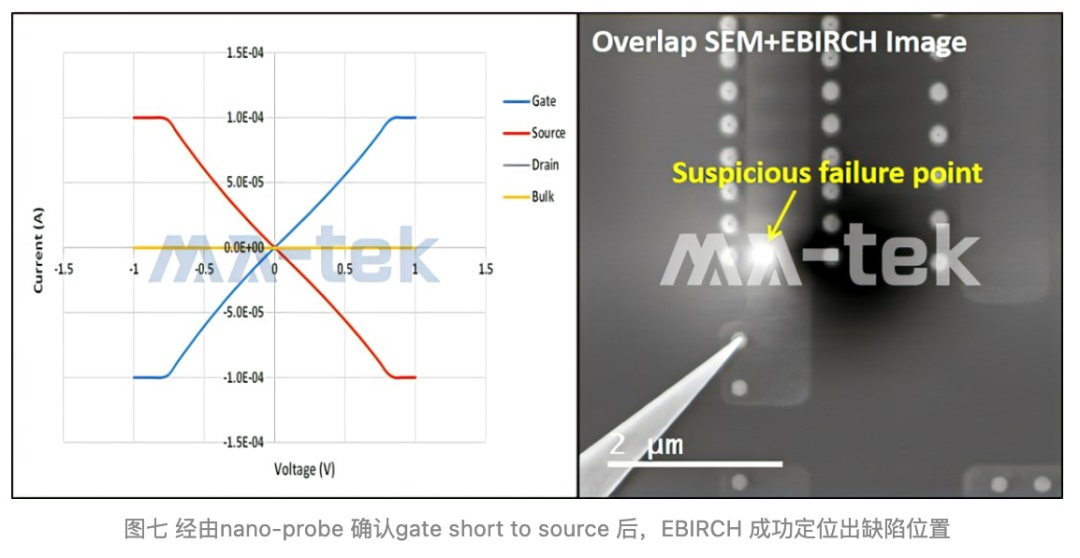

EBIRCH 跟OBIRCH (Optical Beam Induced Resistance Change)的差别在于其激发源为电子束,而非红外光,除此之外原理皆相同,从此便可了解到既然是以电子束为激发源,那么其解析度就比OBIRCH 来得优异。OBIRCH 是下针在die PAD,进行芯片里缺陷的定位,此时还不知道缺陷在何处;而EBIRCH 必须事先知道有问题的讯号线,才可下针在对应的metal line 或via / contact 上,在此前提下可定出精准的缺陷位置,与layout 搭配判断后,即可继续进行样品置备与物性的观察了。 Nano-probe纳米探针量测

Nano-probe纳米探针量测

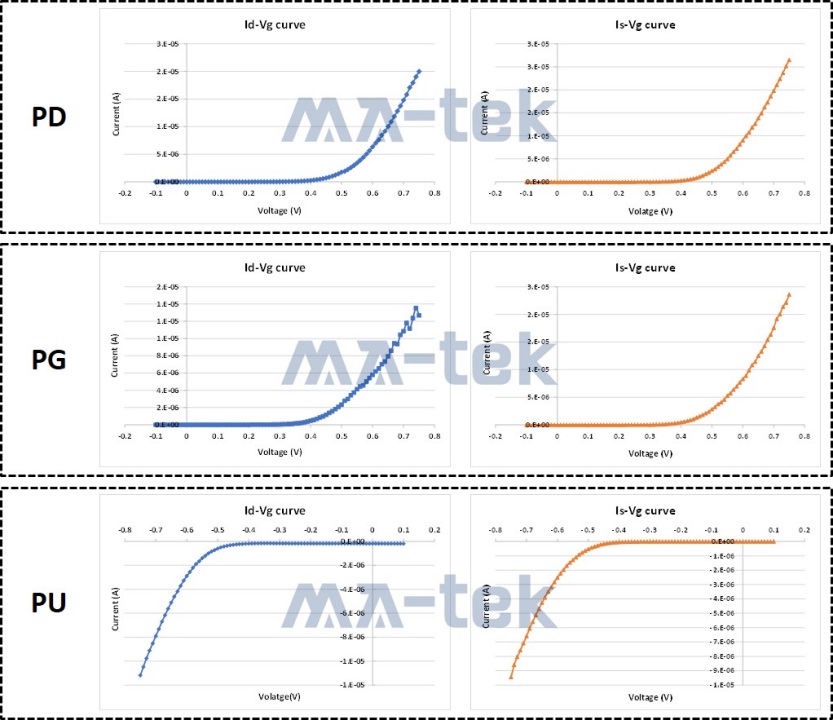

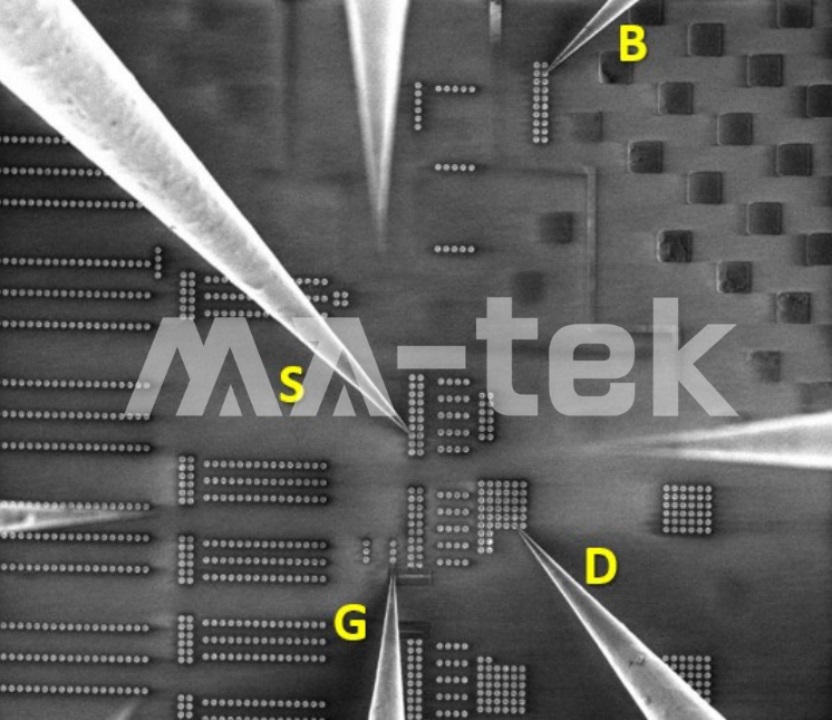

在去层到底层后,有时还找不到缺陷,担心继续下去看不到失效点,平白浪费一个样品吗?那么使用nano-probe 直接量测元件的电性行为,确认漏电路径后便可轻松拟定后续的PFA 步骤。Nano-probe 在SRAM cell 的量测也是不可或缺的工具,虽说直接以plan-view TEM 查找缺陷是个快捷的路径,但以闳康科技在FinFET SRAM 分析将近百颗的经验,有不少的案例是PV TEM 不易看出的,此时借助nano-probe 电性的量测才能判断出异常的位置,进而做出正确截面位置的选择。

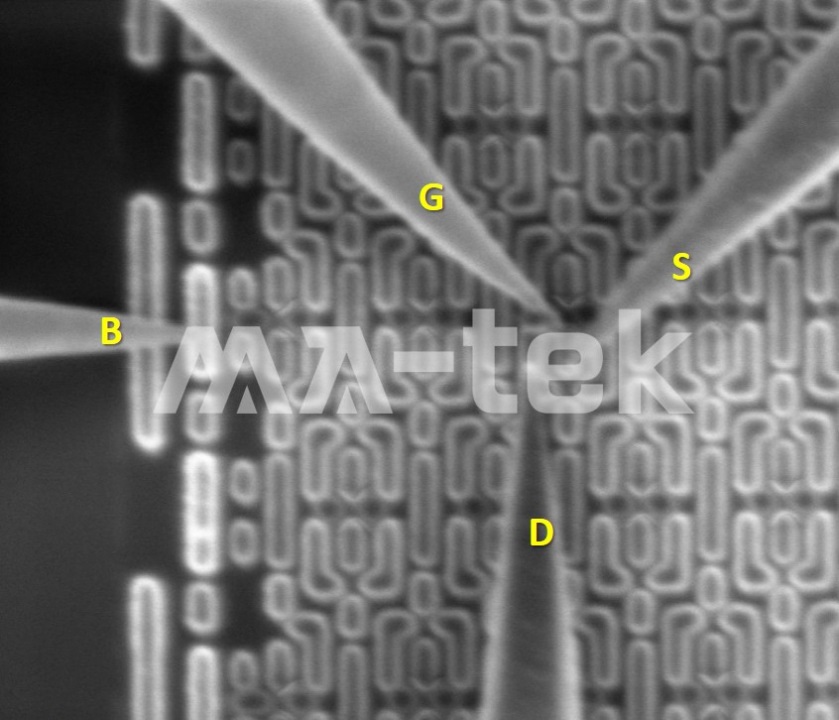

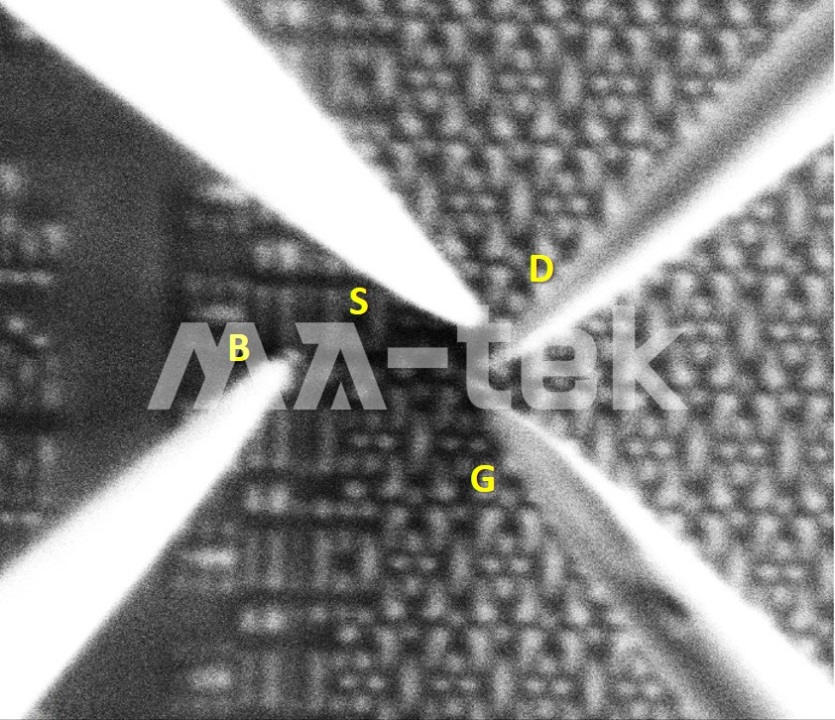

Nano-probe 有两种机型,分别是AFM-based 与SEM-based,闳康在AFM-based nano-probing 经营多年,累积了丰富的经验,已积存了非常可观的nano-probing + PFA 分析资料库。目前量测到12nm FinFET 的成功率接近百分之百,以AFM-based nano-probe 量测的好处是操作效率高,没有电荷累积造成电性飘移的问题,对大多数公司来说仍是首选的机台。随着制程演进到7nm 以下,AFM-based nano-probe 面临到机台的极限,此时 SEM-based nano-probe 便可派上用场。目前闳康与各国际大厂合作,已然量测到5nm 的产品,为其它想要进入7nm / 5nm 制程领域的厂商铺垫了稳固的基石。

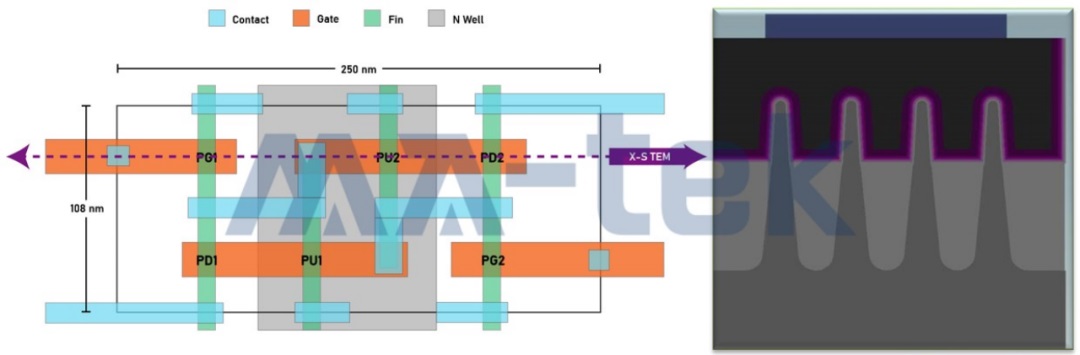

由于FinFET 元件过小,即便已确认缺陷所在位置,也无法用FIB 边切边找缺陷的方式来进行,一方面是解析度的问题,另一方面也可能是缺陷过小而有所遗漏,因此较适合利用高解析度TEM 来观察。以TEM 观察的方式会分成两步骤,第一是先执行PV TEM 做大范围的观察与确认缺陷位置,第二才是针对可疑的缺陷执行XS TEM,虽然分了两道工序,但是大大地提高了分析成功率。此两步骤的TEM 观察法既观察到了平面,也检视了截面,故称之为 3D TEM,此法大量地运用在FinFET 制程上,是整道total-solution FA 的最后关键。 图十二 左图为 FinFET 的平面示意图,以 PV TEM 观察后,选定好切面的位置再转切 XS TEM,右图为 X 方向的切面示意图,目的主要是观察 gate oxide(闸极氧化层)的问题

图十二 左图为 FinFET 的平面示意图,以 PV TEM 观察后,选定好切面的位置再转切 XS TEM,右图为 X 方向的切面示意图,目的主要是观察 gate oxide(闸极氧化层)的问题